Dr Eva Bestelink

About

Biography

Dr Eva Bestelink is a postdoctoral researcher working with Associate Professor Dr Radu Sporea on contact-controlled thin-film transistors and circuits for large area electronics. Her research is mainly focused on source-gated transistors and the multimodal transistor, which she co-invented with Dr Sporea during her second year as an undergraduate BEng EEE student at the University of Surrey.

During her PhD, she won the 2021 IET Postgraduate Prize for Execllence and Innovation in Engineering.

My qualifications

Affiliations and memberships

News

ResearchResearch interests

Eva's research involves exploring contact-controlled transistors and phototransistors in a variety of thin-film technologies, on rigid and flexible substrates. She helps lead several international collaborations, as well as patent commercilaization efforts.

Research interests

Eva's research involves exploring contact-controlled transistors and phototransistors in a variety of thin-film technologies, on rigid and flexible substrates. She helps lead several international collaborations, as well as patent commercilaization efforts.

Teaching

During her PhD at University of Surrey, Eva contributed to teaching activities within the EEE department, assisting with 1st year UG laboratory demonstration for EEE1027 LDPS I and EEE1028 LDPS II modules. She also assisted with supervision of EEE 3017 Year 3 Projects, particularly inlolving device simulation and/or fabrication.In addition, Eva co-supervised SATRO summer placement students for simulation based projects.

Eva and her PhD supervisor, Dr Radu Sporea, jointly presented "Beyond learning outcomes: Synergy through frank experience-based communication,” at ExciTES April, 2019 - Excellence in Teaching Symposium, as well as "Stag Audio - The Online Electronics Lab” at ExciTES 2021, led by Dr George Bairaktaris, during his PhD.

Publications

A neuromorphic optical synapse transistor based on a spectrally tuned floating-gate synapse (STFGS), designed to achieve optoelectronic synaptic behavior, is presented. The device incorporates a heterojunction structure composed of a dinaphtho[2,3-b:2',3'-f]selenopheno[3,2-b]selenophene (DNSS) upper channel and an E)-2-(2-((6-(di-p-tolylamino)-4,4-dimethyl-4H-indeno[1,2-b]thiophen-2-yl)methylene)-3-oxo-2,3-dihydro-1H-inden-1-ylidene)malononitrile (Dta-Inth-IC) floating-gate layer. A parylene dielectric layer strategically positioned between the DNSS and Dta-Inth-IC layers functions as a barrier, enabling selective charge storage within the floating-gate architecture. Synaptic plasticity is analyzed by varying stimulation conditions, such as the on-time, off-time, and pulse number of optical pulses. Long-term potentiation (LTP) is observed with efficient charge trapping in the floating-gate under 660 nm light stimulation. Energy band alignment analysis confirms charge accumulation in Dta-Inth-IC under 660 nm light, while 455 nm light stimulation induced rapid recombination in DNSS. The applicability of artificial neural networks (ANN) based on the potentiation curves obtained from STFGS is evaluated. For this purpose, a convolutional neural network (CNN)-based ANN is designed and performs classification tasks using the Fashion Modified National Institute of Standards and Technology (Fashion MNIST) dataset. Through repeated training, a maximum recognition rate of 91.37% for 660 nm light stimulation is achieved, demonstrating that the STFGS successfully mimics synaptic behavior.

A source-gated transistor (SGT) is a type of thin film transistor (TFT) with unique behaviors. Functionally, the SGT is designed to decrease the saturation voltage at a lower and often more stable saturation current in comparison to a standard TFT, which makes it preferable in some circuit applications. This is achieved by introducing additional effects especially around the source region which differentiate the SGT enough that it cannot be described by a standard TFT compact model. The work presented aims to create the first empirical SGT compact model which may be implemented in DC circuits. This compact model has been developed using the data obtained from an SGT TCAD model.

We investigate a mechanism for greatly improving switching speed in contact-controlled thin-film transistors (TFTs), which have persistently performed much slower than Ohmic contact variants. Separating the mechanisms for charge injection and conduction can result in transient settling times two orders of magnitude lower than existing contact-controlled devices (e.g. source-gated transistor) and even lower than in Ohmic contact TFTs for a given drain current. High speed operation is not necessarily only promoted by the well-studied reduction in contact resistance, but rather by a presence of a pre-charged accumulation layer in the source region. These findings greatly expand the applicability of contact-controlled transistors.

— We present the first physical compact model for an amorphous Silicon source-gated transistor with variable Schottky barrier height. A previously published empirical compact model and TCAD model of a source-gated transistor are used to identify dominant effects present. The compact model is then validated on real device measurements. The compact model aims to operate under common conditions and typically desirable regimes of operation for a source gated transistor, such as the flat saturation regime occurring at a particularly low saturation voltage. The dominant injection mechanisms occur through thermionic and thermionic-filed emission, which are the contact effects present in a source-gated transistor. Thermionic emission tends to be dominant under most common conditions. The model is suitably accurate to be used as a representation of a source-gated transistor in a SPICE simulation. This can be seen as a first step toward analog circuit design with source-gated transistors as compact models enable circuit designers to utilize new and unique devices.

Contact-controlled transistors are rapidly gaining popularity. However, simply using a rectifying source contact often leads to unsatisfactory operation, merely as a thin-film transistor with low drain current and reduced effective mobility. This may cause otherwise promising experiments to be abandoned. Here, data from literature is analyzed in conjunction with devices that have been recently fabricated in polysilicon, organic and oxide semiconductors, highlighting the main factor in achieving good saturation, namely keeping saturation coefficient gamma well below 0.3. Secondary causes of suboptimal electrical characteristics are also discussed. Correct design of these alternative device structures will expedite their adoption for high gain, low-frequency applications in emerging sensor circuits.

Artificial neural networks (ANNs) providing sophisticated, power-efficient classification are finding their way into thin-film electronics. Thin-film technologies require robust, layout-efficient devices with facile manufacturability. Here, we show how the multimodal transistor's (MMT's) transfer characteristic, with linear dependence in saturation, replicates the rectified linear unit (ReLU) activation function of convolutional ANNs (CNNs). Using MATLAB, we evaluate CNN performance using systematically distorted ReLU functions, then substitute measured and simulated MMT transfer characteristics as proxies for ReLU. High classification accuracy is maintained, despite large variations in geometrical and electrical parameters, as CNNs use the same activation functions for training and classification.

The development and optimization of flexible electronics has allowed technology to be better integrated in applications and environments where the physically rigid nature of electronics is previously a limiting factor. Printing techniques contribute to lowering the fabrication costs and making manufacturing-on-demand viable. The use of flexible electronics in the user interface domain has been previously explored with solution-processed optical photodetectors created and the feasibility of using flexible sensors demonstrated in augmented paper applications. In this work, low-cost photodetectors are developed using scalable printing techniques, their electrical performance is analyzed, and their stability over time is studied both in air and in vacuum, the structure is optimized through a combinatorial optimization experiment, and a scalable integration method is demonstrated for creating larger, addressable arrays of detectors. This is a demonstration of how printing methods allow for easy, cost-effective, and low-energy manufacturing of uniform and stable photosensors.

In this roadmap we consider the status and challenges of technologies that use the properties of a rectifying metal-semiconductor interface, known as a Schottky barrier (SB), as an asset for device functionality. We discuss source gated transistors, which allow for excellent electronic characteristics for low power, low frequency environmentally friendly circuits. We also consider reconfigurable field effect transistors. In such devices, two or more independent gate electrodes can be used to program different functionalities at the device level, enabling ultra-secure embedded devices. Both types of transistors can be used for neuromorphic systems, notably by combining them with ferroelectric SB transistors which enable a large number of analog states. At cryogenic temperatures SB transistors can advantageously serve for the control electronics in quantum computing devices. If the source/drain of the metallic contact becomes superconducting, Josephson junctions with a tunable phase can be realized for scalable quantum computing applications. Developing applications using SB devices requires physics-based and compact models that can be used for circuit simulations, which are also discussed. The roadmap reveals that the main challenges for these technologies are improving processing, access to industrial technologies and modeling tools for circuit simulations.

This study aims to increase the output current of the a-IGZO source-gated transistor (SGT) through TCAD simulation and experiment. As SGT proves to be useful in various low-power applications and wearable devices, the low output current characteristics limit the adaptability of this structure. It is estimated that a higher level output current is achievable by optimizing this architecture while retaining fast saturation characteristics. The SGT structure simulations have been performed with adjusted density- of-states (DoS) parameters from experiments; this made TCAD simulation more realistic and can be used to predict the results of fabricated SGTs. The results from this study show that longer source-channel overlap and thinner channel is preferable; the SGT with longer source-channel overlap will result in the Mode II injection dominating over the Mode I injection. The Mode I injection occurs at the edge of source contact near the channel region, while the Mode II injection occurs at the bulk of the source at the farthest region from the channel. The result from experiment shows that the fabricated SGT exhibits Mode II injection characteristics-that is the current will increase linearly with increasing gate voltage. From this study. it could be concluded that the source-channel overlap of 210 µm with a channel thickness of 20 nm and channel length of 5 µm is the optimized structure that could provide high output current with little temperature dependence. Further improvement of the output current could be achieved by utilizing lower work function source metal.

We propose a 5-transistor, 2-capacitor (5T2C) AMOLED pixel circuit using a multimodal transistor (MMT) as driver, which may be more appropriately referred to as 4T1M2C to reflect the inclusion of a device which is distinctly different from conventional Ohmic-contact thin-film transistors (TFTs). The MMT is a type of contact-controlled transistor, here implemented with a Schottky source. Its gating mechanisms separate ‘analog' charge injection, controlled by the source contact, from ‘digital' channel conductance switching. The mixed-signal operation of the MMT allows it to perform the function of multiple conventional transistors in a power- and area-efficient manner, enabling pixel circuit design to achieve superior image uniformity and energy efficiency, due to the combination of threshold compensation scheme and inherent saturation properties of the MMT drive transistor.

Low-temperature microcrystalline silicon ( μ -Si) has been realized in a Corial inductively coupled plasma chemical vapor deposition (ICP-CVD) system. Both doped and undoped μ -Si layers have been investigated in terms of resistivity and crystalline fraction. Following a μ -Si recipe using H 2 /Ar/SiH 4 mixture developed for plasma-enhanced chemical vapor deposition (PECVD), a technological transfer has been carried out in ICP-CVD. Some key parameters have been defined and a domain of use determined for N-type, P-type, and intrinsic layers. In the same reactor, nitride layers have also been deposited to perform gate insulator for thin-film transistors (TFTs). Finally, TFTs were fully realized by ICP-CVD and also electrically characterized, highlighting the interest of ICP-CVD for thin-film electronics. This demonstrates the great versatility of ICP-CVD technology applied to low-temperature electronic processes.

We report the first implementation of a complementary circuit using thin-film source-gated transistors (SGTs). The n-channel and p-channel SGTs were fabricated using the inorganic and organic semiconductors amorphous InGaZnO (IGZO) and dinaphtho[2,3-b:2 & PRIME;,3 & PRIME;-f]thieno[3,2-b]thiophene (DNTT), respectively. The SGTs exhibit flat output characteristics and early saturation (dV(DSAT)/dV(GS) = 0.2 and 0.3, respectively), even in the absence of lateral field-relief structures, thanks to the rectifying source contacts realized with Pt and Ni, respectively. Hence, the complementary inverter shows excellent small-signal gain of 368 V V-1 and noise margin exceeding 94% of the theoretical maximum. We show that the trip point of such inverters can be tuned optically, with interesting applications in compact detectors and sensors. Numerical simulation, using Silvaco ATLAS, reveals that optimized and monolithically-integrated SGT-based complementary inverters may reach a small-signal gain over 9000 V V-1, making them highly suited to low and moderate speed digital thin-film applications. This proof-of-concept demonstration provides encouraging results for further integration and circuit level optimizations.

A multiple-gate transistor comprises a source, a drain spaced apart from the source, a semiconductor region disposed between the source and drain, and an insulating region disposed over the semiconductor region. A current control gate controls a magnitude of current flowing between the source and drain through the semiconductor region in dependence on a first electric field applied to the current control gate, and is separated from the source by the semiconductor region and the insulating region. A switching gate permits current to flow between the source and drain through the semiconductor region in dependence on a second electric field applied to the switching gate. The transistor's conduction state can be controlled by varying the second electric field applied to the switching gate, whilst varying the first electric field that is applied to the current control gate can set the magnitude of the current through the multiple-gate transistor.

Recently, hybrid organic-inorganic perovskites have emerged as promising photo-sensing materials for next-generation solution-processed phototransistors, achieving high responsivity, detectivity, and fast response. Here, a phototransistor that can detect visible light using a low-cost, solution processed methylammonium lead iodide/zinc oxide (CH3NH3PbI3/ZnO) heterostructure is reported. While typical ZnO thin-film transistors (TFTs) do not show any photocurrent under visible light illumination, CH3NH3PbI3 (MAPbI(3)) coated ZnO TFTs exhibit substantial photocurrent. Additionally, the optical, morphological, and structural characteristics of the light-absorbing layers are further controlled by altering the precursor ratio of methylammonium iodide and lead (II) iodide (MAI:PbI2), which in turn affects the photosensitivity. Stoichiometric composition (MAI:PbI2 = 1:1) of MAPbI(3) demonstrates optimal characteristics with a responsivity of 234 A/W and a high detectivity of 3.74 x 10(13) Jones under white light illumination. The high photo-responsivity and detectivity result from the combination of the suitable optoelectronic properties of the stoichiometric MAPbI(3) film and its smooth interface with the ZnO channel.

A Corial Inductively Coupled Plasma Chemical Vapor Deposition (ICP‐CVD) system has been investigated to produce un‐doped and doped μ‐Si layers, as well as insulators, leading to a general capability of performing N and P type TFTs. This enables to develop rapid prototyping of TFTs. Resistivity of layers and TFT issues from ICP‐CVD have been electrically characterized.

A new device, the Multimodal Transistor (MMT), separates charge injection from conduction. With design optimization, it can achieve a constant transconductance with independent on/off switching of output current. This functionality has ample applications in energy efficient analog computation and hardware learning.

Multimodal transistors (MMTs) build on previous understanding of contact‐controlled transistors. Additionally, they allow precise control of the charge injected, distinct from controlling the state of conduction of the semiconductor channel. This approach leads to interesting functionality, of benefit to displays and other large area electronic circuits. Here, we summarize the construction and functionality of the MMT and outline potential applications.

New materials and optimized fabrication techniques have led to steady evolution in large area electronics, yet significant advances come only with new approaches to fundamental device design. The multimodal thin‐film transistor introduced here offers broad functionality resulting from separate control of charge injection and transport, essentially using distinct regions of the active material layer for two complementary device functions, and is material agnostic. The initial implementation uses mature processes to focus on the device's fundamental benefits. A tenfold increase in switching speed, linear input–output dependence, and tolerance to process variations enable low‐distortion amplifiers and signal converters with reduced complexity. Floating gate designs eliminate deleterious drain voltage coupling for superior analog memory or computing. This versatile device introduces major new opportunities for thin‐film technologies, including compact circuits for integrated processing at the edge and energy‐efficient analog computation.

Contact-controlled devices, such as source-gated transistors (SGTs), deliberately use energy barriers at the source, and naturally, the positive temperature dependence (PTD) of drain current can be utilized for temperature sensing. We exploit the difference in drain current activation energy, which arises with contact doping in polysilicon n-type contact-controlled transistors, to demonstrate output current with either a PTD or negative temperature dependence (NTD). The range over which output current varies linearly with temperature, as well as the sensitivity, can be tailored by the choice of reference current magnitude and relative source contact properties within the current mirror. The sensing scheme simplifies the circuit design because it relies solely on thin-film transistors and it has inherent immunity to output voltage variation. This ability to tune the sign of temperature dependence allows facile integration in applications requiring homeostasis via feedback, e.g., electronic skin, in a minimal layout area and potentially with convenient reduction of patterning steps during fabrication.

The first flexible source-gated transistors (SGTs) in microcrystalline silicon have been fabricated and characterized under bending stress. As SGTs are contact controlled devices, the channel does not modulate drain current, however its geometry has implications for operation. We show how reduced channel length in SGTs helps promote negligible threshold voltage shifts when strain is introduced with a radius of r = 2.5 mm.

We have recently demonstrated that, contrary to conventional TFT design rules, emissive pixels based on source‐gated transistor drivers benefit from choosing a source‐gate overlap of several microns. Using TCAD simulations we show that incorporating the SGT overlap capacitance with that of the conventional storage capacitor, pixel area can be optimized, with no adverse impact on data retention. For the technology considered, the optimum source‐gate overlap was 4 ‐ 8 μm, which is in the range of highest operating frequencies for source‐gated transistors.

A novel compact realization of the xnor/xor function is demonstrated with multimodal transistors (MMTs). The multimodal thin-film transistors (MMT's) structure allows efficient use of layout area in an implementation optimized for unipolar thin-film transistor (TFT) technologies, which may serve as a multipurpose element for conventional and emerging large-area electronics. Microcrystalline silicon device fabrication is complemented by physical simulations.

A new device, the Multimodal Transistor (MMT), separates charge injection from conduction and achieves a linear dependence of drain current on its control gate voltage. This functionality is used to implement a highly compact digital‐to‐analog‐converter, capable of performing 3‐level, 3‐bit conversion with minimal error (1.2% of LSB).

Two-transistor zero-VGS amplifiers made with polysilicon source-gated transistors achieve voltage gain approaching 300 (49dB). TCAD simulations reveal the effect of load and driver transistor geometry on gain and operating frequency. The SGT circuits have simultaneously superior gain and reduced layout area (two-transistor, channel length L = 3μm and width W = 10 and 30μm), relative to conventional TFT implementations. These results recommend low-complexity, compact SGT designs for flexible and printed amplifiers, such as bio- and chemical sensors.

We describe the physics of the turn-off mechanism in source-gated transistors (SGTs), which is distinct from that of conventional thin-film field-effect transistors and allows significantly lower off currents, particularly in depletion-mode devices. The “n-type” SGT enters its off state when the potential applied across the semiconductor layer is decreased to low positive values or made negative through the applied gate bias, thus impeding charge injection from the source contact. Measurements on polysilicon devices were supported with TCAD simulations using Silvaco Atlas. Alongside the other known benefits of SGTs, including low saturation voltage, tolerance to process variations, and high intrinsic gain, the ability to efficiently block current at high negative gate voltages suggests that these devices would be ideal elements in emerging thin-film power management and rectification circuits.

Silicon-based digital electronics have evolved over decades through an aggressive scaling process following Moore’s law with increasingly complex device structures. Simultaneously, large-area electronics have continued to rely on the same field-effect transistor structure with minimal evolution. This limitation has resulted in less than ideal circuit designs, with increased complexity to account for shortcomings in material properties and process control. At present, this situation is holding back the development of novel systems required for printed and flexible electronic applications beyond the Internet of Things. In this work we demonstrate the opportunity offered by the source-gated transistor’s unique properties for low-cost, highly functional large-area applications in two extremely compact circuit blocks. Polysilicon common-source amplifiers show 49 dB gain, the highest reported for a twotransistor unipolar circuit. Current mirrors fabricated in polysilicon and InGaZnO have, in addition to excellent current copying performance, the ability to control the temperature dependence (degrees of positive, neutral or negative) of output current solely by choice of relative transistor geometry, giving further flexibility to the design engineer. Application examples are proposed, including local amplification of sensor output for improved signal integrity, as well as temperature-regulated delay stages and timing circuits for homeostatic operation in future wearables. Numerous applications will benefit from these highly competitive compact circuit designs with robust performance, improved energy efficiency and tolerance to geometrical variations: sensor front-ends, temperature sensors, pixel drivers, bias analog blocks and high-gain amplifiers.

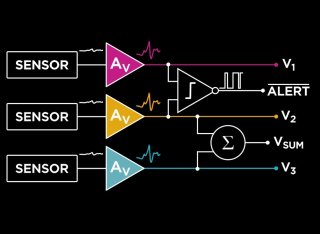

Thin-film transistors deliberately comprising rectifying source contacts have attractive properties for sensor and driver circuits: high performance uniformity and geometrical tolerance; superior saturation; and high intrinsic gain. The paper reviews the source-gated and multimodal thin-film transistor configurations, and presents their proposed applications to ultra-compact sensing and data processing circuits. Source-gated transistors with nanoscale tunneling contacts offer an alternative to the Schottky-contact fabrication route, which presents processing challenges. Emerging multimodal transistors overcome limitations of traditional contact-controlled devices and add to the list of useful properties: high gain or constant transconductance by design; immunity to drain voltage variations in floating gate configuration; and a significantly faster response time than source-gated transistors. These devices form the foundation for the design of compact, yet extremely versatile, thin-film circuits for sensing, signal conditioning and signal conversion. Finally, a vision is presented in which the properties of these circuits will be essential to convey seamless user interactivity to physical objects, transforming them into intuitive user interfaces beyond traditional displays screens.

Despite rapidly expanding interest in thin-film source-gated transistors (SGTs), the high temperature dependence of drain current (TDDC) in devices comprising Schottky source barriers is delaying wide adoption. To reduce this effect, alternative source designs have been theorized. Specifically, introducing additional nanoscale layers at the source contact should facilitate tunneling of charge carriers at the Fermi energy level with negligible TDDC. Here, we fabricate amorphous In₂Ga₂ZnO₇ tunnel-contact SGTs (TCSGTs) with three times lower TDDC than polysilicon transistors with Schottky contacts. Numerical simulations help elucidate the control mechanisms. We show that the potential profile across the semiconductor in the bulk of the source-gate overlap region determines injection current, and the introduction of a thin interfacial layer at the contact reduces the role of the contact metal work function in current control and associated temperature effects. This device architecture adds improved thermal stability to the long list of SGT benefits, including low voltage saturation, power-efficient operation, high intrinsic gain, device-to-device uniformity, and robustness to mechanical and electrical stress.

Many emerging analog and neuromorphic applications would benefit from a fully linear dependence of a transistor's output on its input for reduced distortion and facile design of linear functions. We show how a new TFT structure, the multimodal transistor, can achieve a linearly dependent drain current in saturation (constant transconductance) with direct proportionality over a large range of input voltages.

Contrary to conventional design principles, currentdriven pixel drivers based on source-gated transistors (SGTs) achieve their optimal drive current and speed with a deliberate 5 -10μm gate-source overlap. Total pixel circuit area need not increase, as the additional device area can be compensated by reducing the pixel storage capacitor. Numerical simulations demonstrate the viability of SGTs for emissive pixel drivers and high gain, low power, robust circuits for emerging sensor arrays.

Hot-carrier effects are a persistent challenge for Ohmic contact, high carrier mobility thin-film transistors. As semiconductor properties are systematically improved, such phenomena (e.g., the kink effect) are becoming apparent even in materials such as InGaZnO. Few of the past solutions are practical in these low-complexity semiconductor systems. Here, it is shown that contact-controlled devices offer robust performance under extreme biasing conditions due to their distinctive charge injection processes. The recently-developed multimodal transistor (MMT) provides further control still, by separate regulation of current flow and magnitude. Internal electric field distributions in the source and drain regions are studied via technology computer-aided design simulations, and support the formulation of operational guidelines for the MMT's channel control gate for optimal characteristics in saturation. As MMT principles are universal, these findings should inform device design and operation in all high carrier mobility material systems.

Low saturation voltages and extremely high intrinsic gain can be achieved in contact-controlled thin-film transistors (TFTs) with staggered device architecture, enabled by the energy barrier introduced at the source contact. The resulting device, the source-gated transistor (SGT), is limited in its usefulness by the high temperature dependence of the drain current induced by the source energy barrier. Here, the interaction between the thermal characteristics of the source contact and the semiconductor to show drastically reduced temperature dependence for SGTs based on organic semiconductors (OSGTs) is exploited. This extraordinarily weak temperature dependence of the drain current is observed regardless of the height of the source energy barrier (27.8% in OSGTs with Ti contacts compared to 22.1% when using Au contacts, over a 34 K range). The reduction in mobility of the semiconductor offsets an increase in thermionic-field emission of charge carriers at the source. This is a first for SGTs and provides a route to removing one of the last hurdles to their wider adoption. The OSGTs with Ti contacts also demonstrate: drain-current saturation at very low drain-source voltages (saturation factor of 0.22); noteworthy stability after 70 days; and minimal drain-current variation with channel length or illumination.